- Home

- Hardware

- SDKs

- Cloud

- Solutions

- Support

- Ecosystem

- Company

- Contact

news

ESP32-P4 Chip Upgrade: Performance and Multimedia Experience Enhancement

Shanghai, China

May 8, 2026

Users currently developing or producing with the ESP32-P4 should upgrade their firmware and hardware designs as soon as possible.

Espressif Systems (688018.SH) has officially released ESP32-P4 chip version v3.x, delivering significant upgrades in clock speed, image processing, power management, and security. This new version significantly enhances high-performance HMI, edge computing, and smart IoT applications. We strongly encourage users currently developing or producing with the ESP32-P4 to upgrade their firmware and hardware designs promptly.

Why Upgrade

ESP32-P4 v3.x significantly enhances processing performance, delivering a stable maximum clock speed of 400 MHz. The update also introduces major upgrades to multimedia modules—including ISP and PPA—while resolving known issues from earlier versions, such as MSPI power-on wake-up errors (Load access fault) and secure boot verification failures. These improvements enable developers to achieve higher performance in applications demanding superior image quality and fast response times.

-

Improved Computing Performance: The dual-core RISC-V processor in the high-performance (HP) system now reaches a maximum clock speed of 400 MHz (up from 360 MHz). New support for Zb bit manipulation extensions and optimized PIE acceleration units significantly enhance device efficiency in complex algorithms and real-time data processing.

-

Enhanced Multimedia Experience: The Image Signal Processor (ISP) now includes Black level correction (BLC), Dead pixel correction (DPC), White balance gain (WBG) and Cropping (CROP). These features ensure high-quality image in various lighting conditions. The Pixel Processing Accelerator (PPA) now supports processing blocks of 32x32 and adds broad support for formats like YUV422/YUV420, improving UI and video fluidity. A 160 MHz clock source has been added for I2S, fully meeting the needs of state-of-the-art audio applications.

-

Strengthened Security Protection: The AES accelerator now includes pseudo-round Differential Power Analysis (DPA) resistance to effectively counter side-channel attacks. The ECC accelerator now supports higher-level P-384 elliptic curves. A dedicated Random Number Generator (RNG) module has been introduced, providing stronger protection for security-sensitive applications.

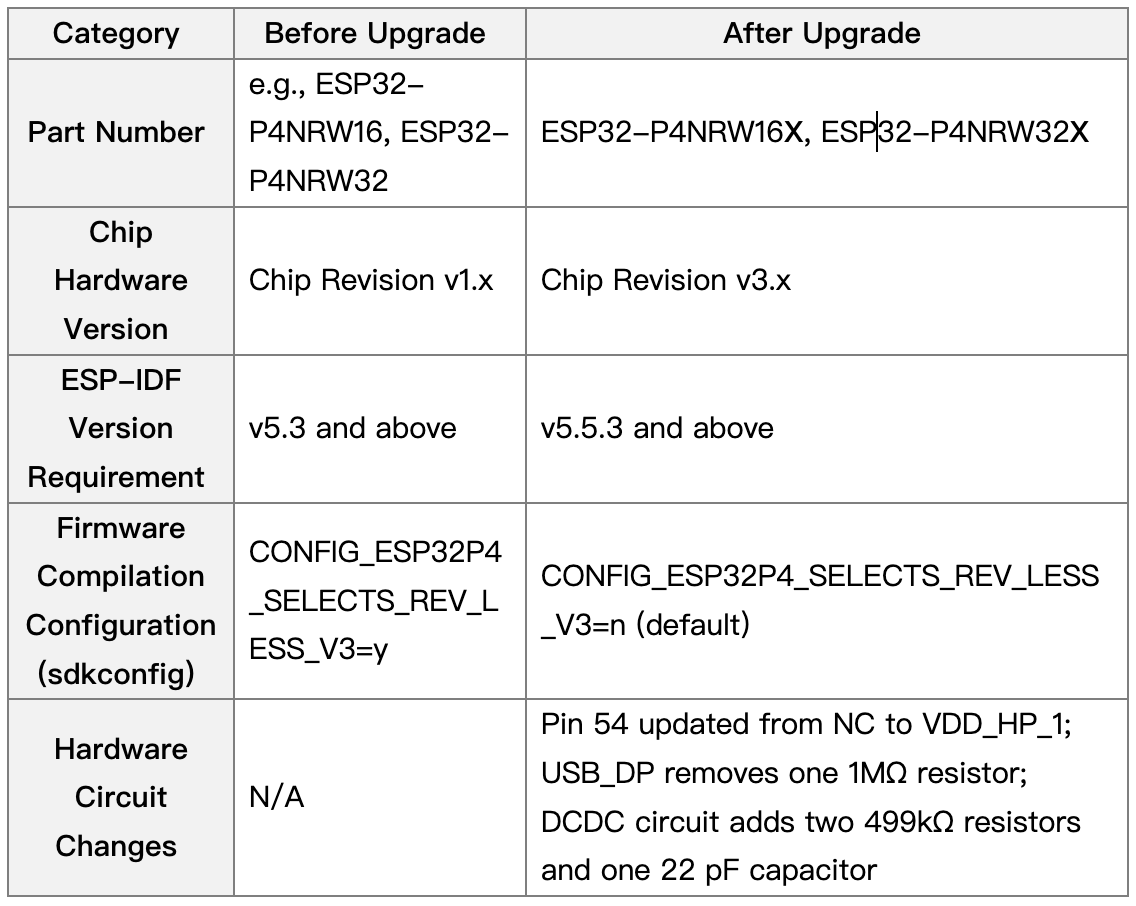

Product Upgrade Comparison Table

Support and Additional Information

For detailed design changes, technical specifications, and migration guides for ESP32-P4 chip version v3.x, refer to the following official resources:

-

ESP32-P4 Chip Version v3.x User Guide: Covers major changes from v1.x, impact on customer projects (firmware and hardware upgrade requirements), and silkscreen identification specifications.

-

ESP32-P4 Datasheet: Provides the latest specifications for electrical characteristics, pin definitions, and functional descriptions.

-

ESP32-P4 Technical Reference Manual (TRM): Includes detailed register descriptions and operational details for the high-performance processor, ISP, 2D-DMA, H.264 encoder, and security accelerators.

-

ESP32-P4 Chip Errata: Lists hardware issues fixed in v3.x, such as MSPI access errors, secure boot verification anomalies, and DMA conflicts.

If you have technical questions during the upgrade, please contact our technical support team through the Espressif Customer Support Page or submit feedback on the ESP-IDF GitHub.

LinkedIn

LinkedIn 微信

微信

Twitter

Twitter Facebook

Facebook